Tak czy siak, wbrew pozorom - optymalizowanie czasów przełączania w DRSSTC mija się z celem.

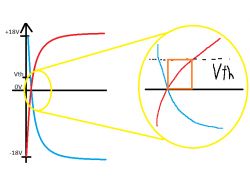

Primo, mamy ZCS - i ZCS jest wszystkim. Jak długo masz dobry phase lead i przełączanie kluczy jest centrowane mniej więcej w okół zera prądu cała reszta jest bez znaczenia. Straty przełączania są pomijalne, więc żyłowanie czasów przełączania nie znaczenia. Dioda równoległa nie przewodzi praktycznie w cale w trakcie dead time, więc nie musi on być optymalny. A od ZCS nie uciekniesz bo zabiją Cię albo przepięcia, albo ogon prądowy.

A ponadto... Stosując duże moduły IGBT

nie chcesz aby przełączały się zbyt szybko! Dlaczego? Otóż:

-Jak długo jesteś w ZCS, OK, ale jeżeli z jakiegokolwiek powodu przełączysz się przy dużym prądzie, zbyt szybkie przełączenie wyindukuje transjent na wewnętrznych indukcyjnościach modułu IGBT (które, nomen omen, nie są takie małe, no bo w końcu cały moduł jest duży). Ten transjent jest w stanie zabić klucz i nie ma

żadnej metody na jego kontrolę, oprócz ograniczenia szybkości przełączania i/lub prądu w jego trakcie.

-Nawet najnowocześniejsze IGBT potrafią się zatrzasnąć jak przesadzisz z dI/dt.

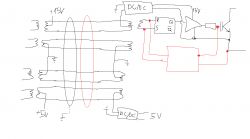

Tak samo nie stosuje się adaptatywnego dead time w energoelektronice HV/HC, bo to nie ma sensu:

-W starej generacji tranzystorów straty były zdominowane przez przełączanie i przewodzenie, super optymalizacja DT nie dawała miarodajnego zysku, a komplikowała układ. Szukając optymalizacji strat, znacznie lepszym pomysłem był umiarkowanie krótki dead-time i przełączanie rezonansowe - gdzie żyłowanie DT nie ma sensu z tego samego powodu, co w przykładzie DRSSTC.

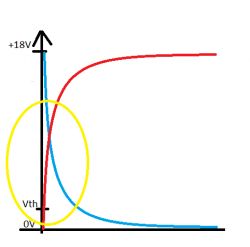

-W najnowszych generacjach półprzewodników, gdzie straty i czasy przełączań spadają do coraz niższych wartości, pasożytnicze diody mają nad wyraz wysokie napięcie przewodzenia, a całość pracuje z coraz większymi częstotliwościami - optymalizacja DT znów ma znaczenie, jako że dioda pasożytniczą będzie zwyczajnie generować znacznie więcej strat przewodzenia niż klucz. Trzeba więc zapewnić, że pracuje tak krótką część okresu, jak się da. Ale... Zarówno współczesne tranzystory jak i drivery do nich mają dobrze scharakteryzowane, przewidywalne zależności czasowe. Więc łatwiej i praktycznie z takim samym rezultatem można ustawić dead time na sztywno z korekcją na niepewność czasową sterownika i zapomnieć o temacie.

-Adaptacyjny dead time to nie panaceum - jego pętla kontrolna musi wziąć korektę na swoje opóźnienie oraz, co gorsza - rozrzut opóźnień. Oznacza to, że tak czy siak musisz narzucić stały DT który zapewnia margines bezpieczeństwa korygujący niepewności czasowe sterowania.... I wracasz do punktu wyżej, gdzie możesz ustawić DT na sztywno bo zachowanie całe układu staje się przewidywalne. Dolicz do tego równania konieczność zapewnienia odporności na glitche w momencie, w którym pętla nie przełączy się idealnie. W elektroenergetyce, dobry DT, to dobrze policzony DT... Który nie polega na ekstra delikatnej pętli wprowadzającej niebezpieczny failure point oferując zysk w promilach.

Układy LV, gdzie adaptację DT się stosuje nagminnie, to troszkę inna para kaloszy jednak.

-Primo - bezproblemowo możesz zaimplementować absurdalnie szybką pętlę kontrolną DT która jest bezpośrednio sprzężona z tranzystorami. Jest więc ona przewidywalna i niezawodna.

-Po drugie, niskonapięciowe (20-30V) MOSFET oferują absurdalnie niskie czasy przełączania i równie absurdalnie niskie RDSon. W tym zakresie implementowanie mostków które przełączają kilkadziesiąt amperów ze zboczem poniżej 1.5ns i rdson w zakresie pojedynczych miliiomów to dla mnie codzienność. I nie tylko na mnie - zajrzyjcie sobie na mobo współczesnych komputerów.

I tu, faktycznie - każda nanosekunda w której dioda nie przewodzi jest cenna i można o nie walczyć. Ale to przypadek skrajny.

Do optymalizacji energoelektroniki wielkiej mocy nie tędy droga. Do tego służą inne podejścia.